SRK02 specifications

General information

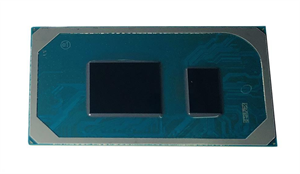

Type CPU / Microprocessor

Family Intel Core i7 Mobile

Processor number ? i7-1165G7

Part number FH8069004530104

Frequency 2.8 GHz

Maximum Turbo frequency 4.7 GHz

Clock multiplier ? 28

Package type 1449-ball FC-BGA

Socket type BGA1449

Architecture / Microarchitecture / Other

Core stepping B1

Processor core Tiger Lake UP3

Manufacturing technology 0.010 micron

The number of cores 4

The number of threads 8

L2 cache size ? 5 MB

L3 cache size 12 MB

Features AES

AVX

AVX2

AVX512

CFET

DLB

EM64T technology ?

Execute disable bit ?

GNA2

Hyper-Threading technology

MMX

SSE

SSE2

SSE3

SSE4

SSSE3

Turbo Boost technology

Virtualization technology (VT-d)

Virtualization technology (VT-x)

Thermal Design Power ? 28 Watt

Notes on sSpec SRK02

The processor supports DDR4-3200 memory.

Frequency of integrated graphics controller in turbo mode is 1300 MHz.

The part supports LPDDR4X-4267 memory.

SRK02 CPUID information

Intel Core i7 Mobile i7-1165G7 SRK02

Part number: FH8069004530104

Measured Frequency: 2803 MHz

Comment:

Submitted by: goodeegg

General information

Vendor: GenuineIntel

Processor name (BIOS): 11th Gen Intel(R) Core(TM) i7-1165G7 @ 2.80GHz

Cores: 4

Logical processors: 8

Base frequency: 2800 MHz

Maximum frequency: 4700 MHz

Bus / reference frequency: 100 MHz

Processor type: Original OEM Processor

CPUID signature: 806C1

Family: 6 (06h)

Model: 140 (08Ch)

Stepping: 1 (01h)

Socket: X0600 (0)

TLB/Cache details: 64-byte Prefetching

Cache details

Cache: L1 data L1 instruction L2 L3

Size: 4 x 48 KB 4 x 32 KB 4 x 1 MB 12 MB

Associativity: 12-way set

associative 8-way set

associative 20-way set

associative 12-way set

associative

Line size: 64 bytes 64 bytes 64 bytes 64 bytes

Comments: Direct-mapped Direct-mapped Non-inclusive

Direct-mapped Non-inclusive

Shared between all cores

Supported instructions

Instruction set extensions Additional instructions

MMX ADCX/ADOX instructions

SSE Advanced Bit manipulation

SSE2 CLFLUSH

SSE3 CLFLUSHOPT

SSSE3 CLWB

SSE4.1 CMOV

SSE4.2 CMPXCHG16B

AES CMPXCHG8B

AVX Enhanced REP MOVSB/STOSB

AVX2 FXSAVE/FXRSTORE

BMI1 INVPCID

BMI2 MONITOR/MWAIT

F16C MOVBE

FMA MOVDIR64B

GFNI MOVDIRI

Supervisor-Mode Access Prevention and CLAC / STAC instructions PCLMULDQ

Supervisor Mode Execution Protection POPCNT

AVX-512 (AVX512 Foundation) PREFETCH/PREFETCHW

AVX-512 (AVX512BITALG) RD/WR FSGSBASE instructions

AVX-512 (AVX512BW) RDRAND

AVX-512 (AVX512CD) RDSEED

AVX-512 (AVX512DQ) RDTSCP

AVX-512 (AVX512IFMA) Read Processor ID

AVX-512 (AVX512VBMI) SYSENTER/SYSEXIT

AVX-512 (AVX512VBMI2) XSAVE/XRESTORE states

AVX-512 (AVX512VL) XSETBV/XGETBV are enabled

AVX-512 (AVX512VNNI)

AVX-512 (AVX512VP2INTERSECT)

AVX-512 (AVX512VPOPCNTDQ)

Secure Hash Algorithm extensions (SHA)

Integrated features and technologies

Major features Other features

On-chip Floating Point Unit 1 GB large page support

64-bit / Intel 64 36-bit page-size extensions

NX bit/XD-bit 64-bit debug store

Hyper-Threading Technology Advanced programmable interrupt controller

Intel Virtualization CPL qualified debug store

Turbo Boost Clock modulation duty cycle extension

Turbo Boost 3.0 Debug store

Enhanced SpeedStep Debugging extensions

Digital Thermal Sensor capability

Extended xAPIC support

Intel Processor Trace

Key Locker

LAHF/SAHF support in 64-bit mode

Machine check architecture

Machine check exception

Memory-type range registers

Model-specific registers

Package thermal management

Page attribute table

Page global extension

Page-size extensions (4MB pages)

Pending break enable

Perfmon and Debug capability

Physical address extensions

Platform Quality of Service Enforcement

Power Limit Notification capability

Process context identifiers

Protection keys for user-mode pages

Self-snoop

TSC rate is ensured to be invariant across all states

Thermal monitor

Thermal monitor 2

Thermal monitor and software controlled clock facilities

Time stamp counter

Timestamp counter deadline

User-mode instruction prevention

Virtual 8086-mode enhancements

xTPR Update Control